www.edn.com

Tales from the Cube Pg 90

Oil prices, technology, and the cost of ignorance Pg 10

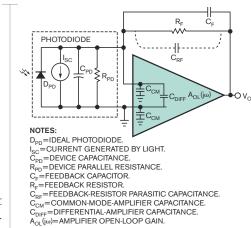

Transimpedanceamplifier stability is key Pg 24

Prying Eyes Pg 26

Design Ideas Pg 71

Page 40

SHEDDING LIGHT ON EMBEDDED DEBUGGING

Page 29

USING FPGAS IN CONSUMER ELECTRONICS

VOICE OF THE ENGINEER

Page 49

OPTIMIZE MEMORY-SYSTEM DESIGN FOR MULTIMEDIA APPLICATIONS

Page 59

RENEW

your FREE **magazine** subscription START

a FREE **e-newsletter** subscription

## The New Oscilloscope Experience Is Here

## Quick Insight. Deep Insight.

Experience the New LeCroy Oscilloscopes.

www.insightwithconfidence.com

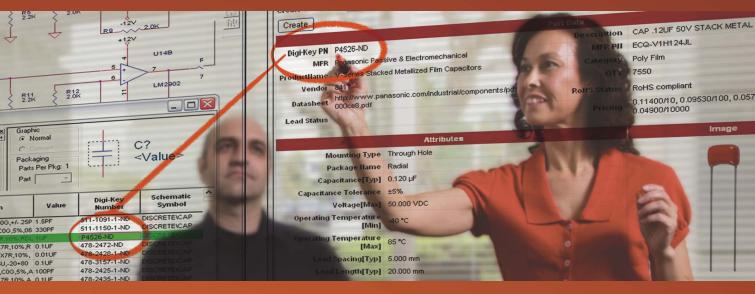

www.digikey.com today to see how many!

Quality Electronic Components, Superior Service

**Digi-Key Corporation purchases all product** directly from its original manufacturer.

www.digikey.com 1.800.344.4539

701 Brooks Ave. South • Thief River Falls, MN 56701 • USA

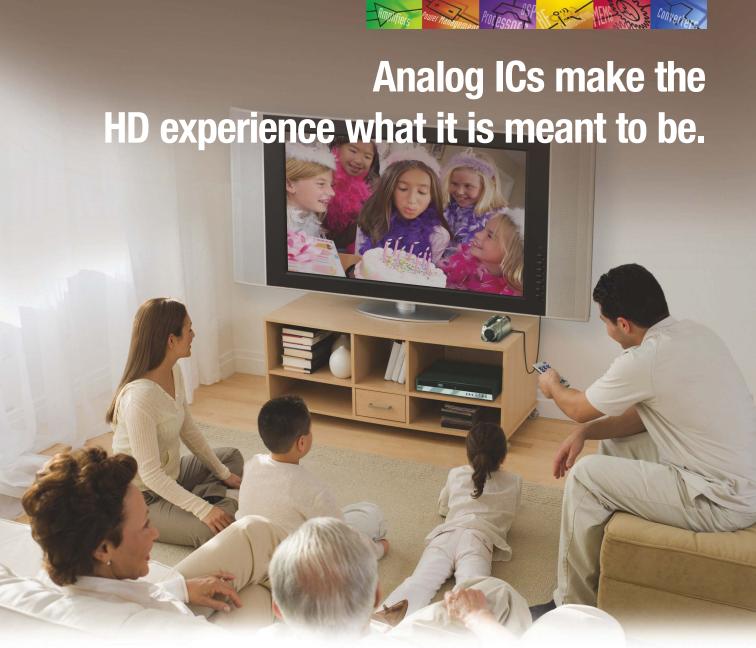

## Home Theater: It's Our Specialty

NORTH AMERICA

+1 800-625-4084

ASIA PACIFIC

+852 2376-0801

JAPAN

+81 (3) 5226-7757

EUROPE/UK

+44 (0) 1628-891-300

Cirrus Logic knows home theater. You might say it's our specialty. Our families of audio DSPs are designed for audio applications—no general purpose processors here. Select from a variety of single or dual-core 32-bit processors that are right for you, with a comprehensive firmware library, along with the industry's widest selection of audio converters that offer the right level of performance and features.

#### CS49700 FEATURES

- 32-bit dual-core audio DSP

- Ideal for Blu-ray® Disc home theater audio

- Multistandard HD decoding + post processing

WWW.CITTUS.COM

Cirrus Logic. We make it easier for you.

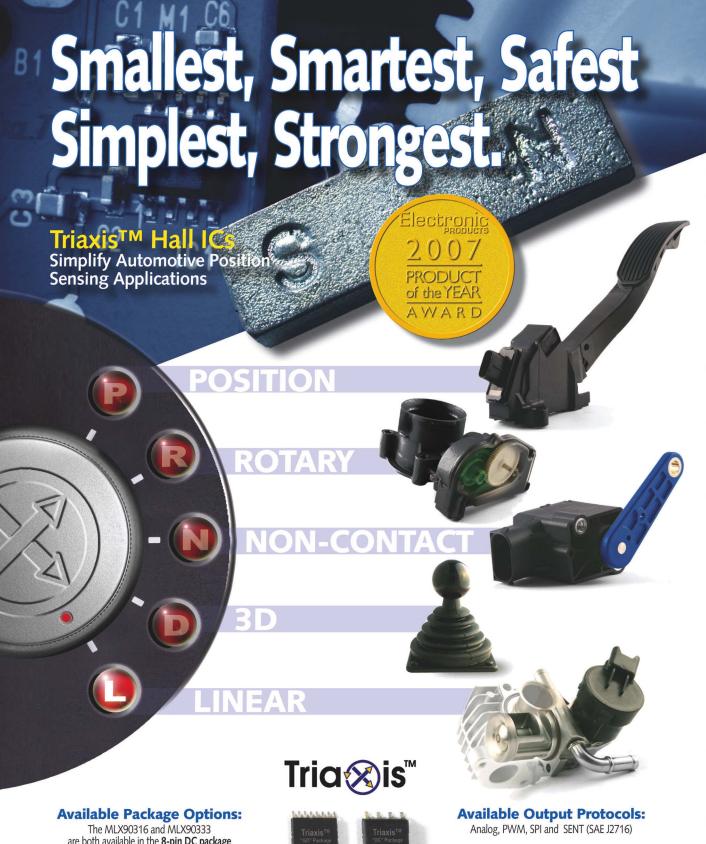

Automotive Sensors

Circuit Protection Solutions

Magnetic Products

Microelectronic Modules

Panel Controls & Encoders

Precision Potentiometers

Resistive Products

## How Will You Protect Your Circuits?

Circuit protection is a crucial part of any design decision today.

No one understands that better than Bourns. We have developed the industry's broadest line of circuit protection solutions – backed by a global team of technical experts. Our customers are assured of finding the optimal solution for their application with Bourns' collective knowledge from years of circuit protection support.

Beyond product depth and support, we have innovative new technologies that solve tough design challenges. Bourns' new gated thyristors provide faster and more efficient protection that reduces costs. Our symmetric gas discharge tubes regulate breakdown voltage innovatively. And Bourns' new polymer PTCs overcome voltage variability to extend product life. In the New World of Bourns, we have the technology to protect your circuits.

www.bourns.com/circuitprotection

Bourns - the company you have relied on for more than 60 years.

Built on Trust...Based on Innovation

## **Green Engineering**

## Powered by National Instruments

Acquire environmental data from thousands of sensors

Analyze power quality and consumption

Present measured data to adhere to regulations

**FIX IT**

**Design** and model more energy efficient machines

Prototype next-generation energy technologies

**Deploy** advanced controllers to optimize existing equipment

For more than 30 years, National Instruments has empowered engineers and scientists to measure, diagnose, and solve some of the world's most complex challenges. Now, through the NI graphical system design platform, engineers and scientists are using modular hardware and flexible software to not only test and measure but also fix inefficient products and processes by rapidly designing, prototyping, and deploying new machines, technologies, and methods. Today, a number of the world's most pressing issues are being addressed through green engineering applications powered by NI products.

>> Download green engineering resources at ni.com/greenengineering

800 890 1345

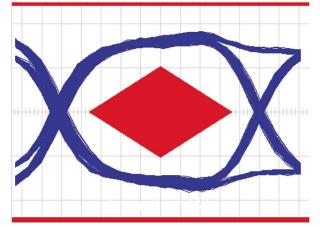

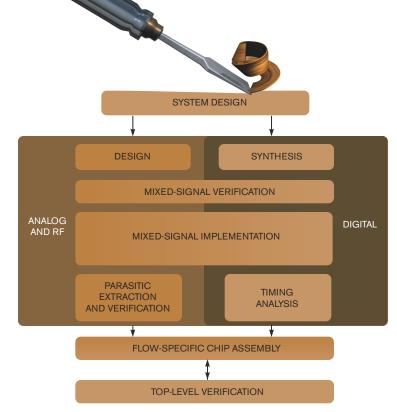

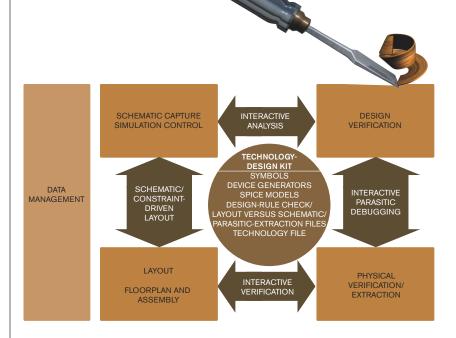

#### Handcrafted analog gets automated assist

EDA tools address simulation, verification, and layout for mixedsignal designs.

by Rick Nelson, Editor-in-Chief

#### Shedding light on embedded debugging

Embedded debugging gets a lot of attention for being a schedule and resource hog, but there may be more to it than just fixing bad by Robert Cravotta, software. Technical Editor

## EDN contents

9.4.08

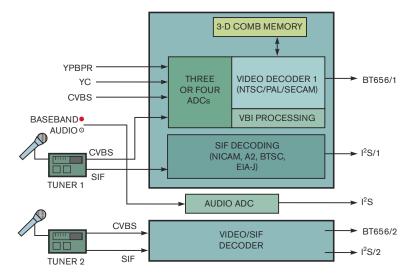

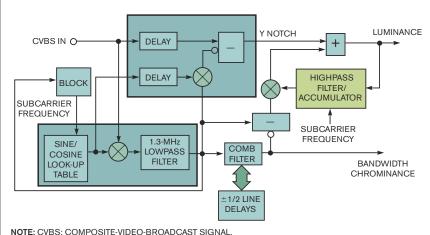

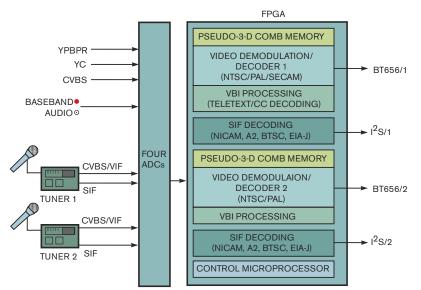

#### Using FPGAs in consumer electronics

In cost-sensitive consumer-electronics products, customization is a highly desirable feature for differentiating your product from competitors' offerings. The inclusion of FPGAs can be affordable, even in low-range and midrange products, but still allows customization through some unique features.

by Phuttachad Thiencharoenwong, SingMai Electronics

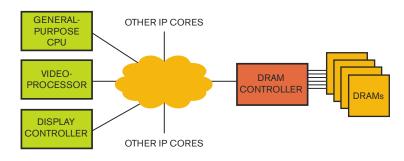

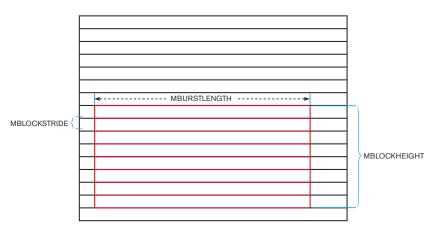

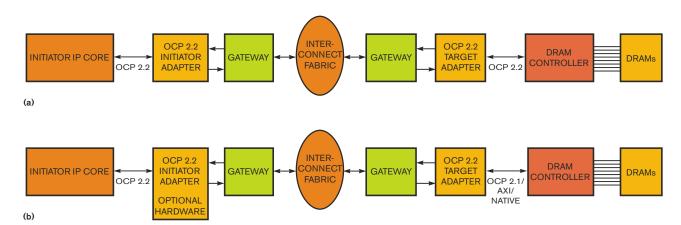

#### Optimize memorysystem design for multimedia applications

The convergence of video and communications in inexpensive unified-memory architectures has made DRAM the most important and the highest-performance target in any system.

> by David Lautzenheiser and Agha Hussain, Silistix

## DESIGNIDEAS

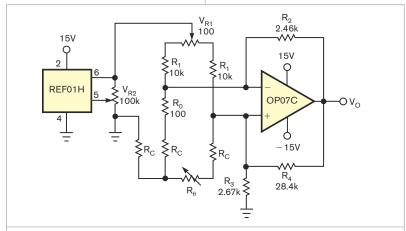

- Platinum-RTD-based circuit provides high performance with few components

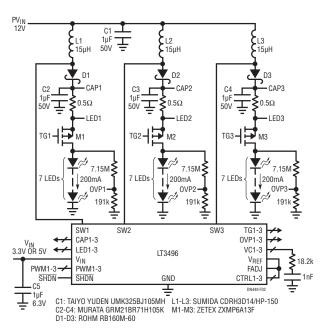

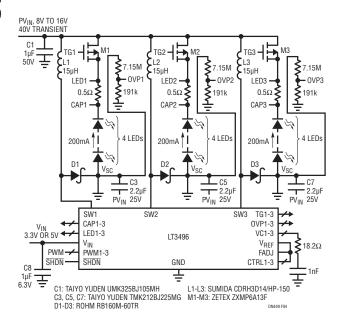

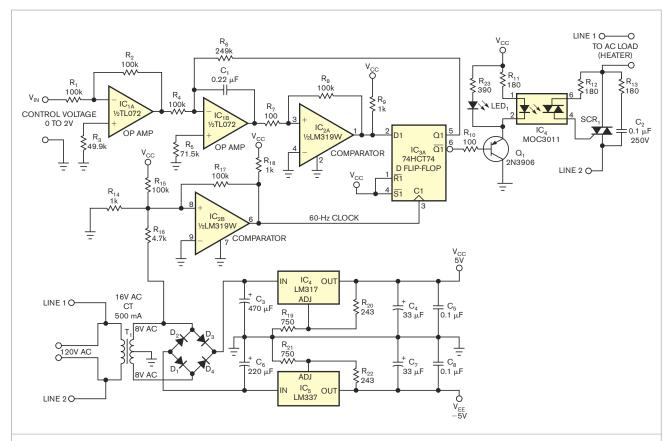

- 72 Proportional-ac-power controller doles out whole cycles of ac line

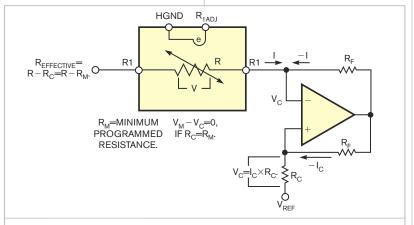

- 78 Extend monolithic programmable-resistor-adjustment range with active negative resistance

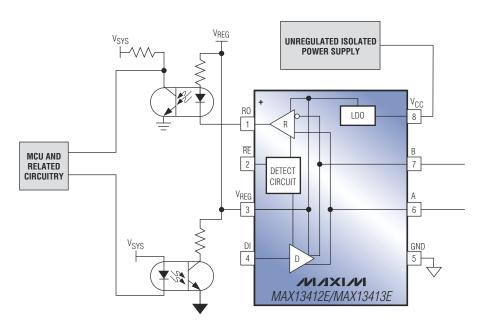

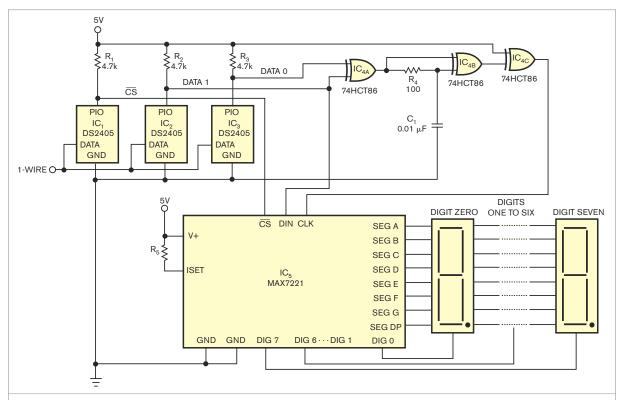

- 78 1-Wire network controls remote SPI peripherals

#### WHAT DO WE HAVE TO DO, DRAW YOU A PICTURE?

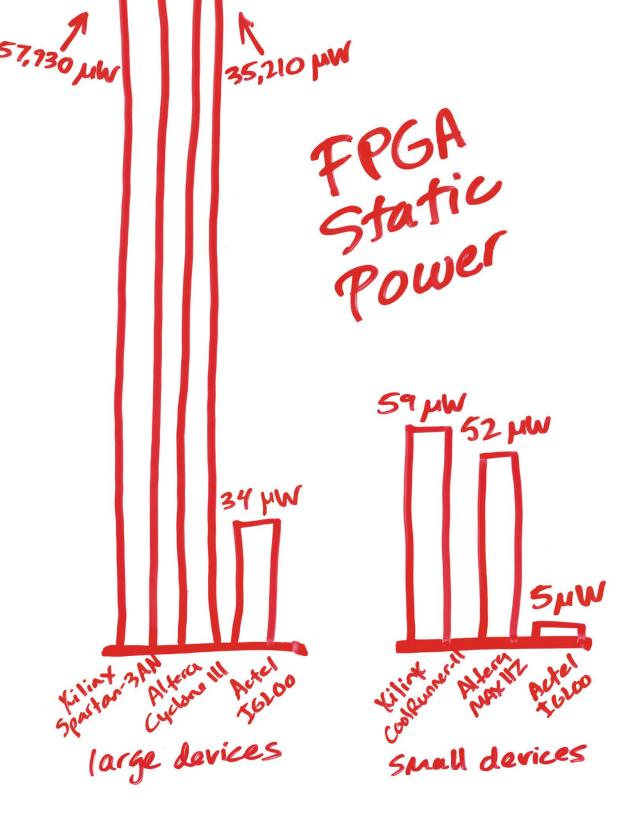

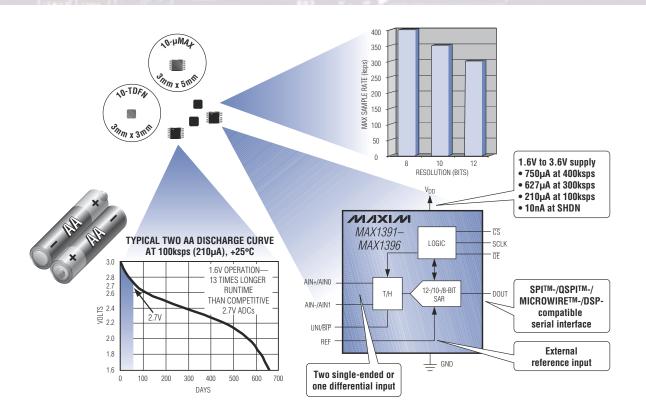

Only Actel gets you this close to zero. Any other claims of low power superiority are just that. According to their own data, Altera® and Xilinx® use between 10 and 1700 times the power of Actel IGLOO® FPGAs, depending on device and mode. Want specifics? Visit us to get the whole picture, including a video of actual measurements.

## contents 9.4.08

- 15 Video, graphics module drives dual displays

- 15 AMD updates Stream software-development kit

- 16 Touch-panel controller targets media-device interfaces

- 16 Module targets embedded-system design

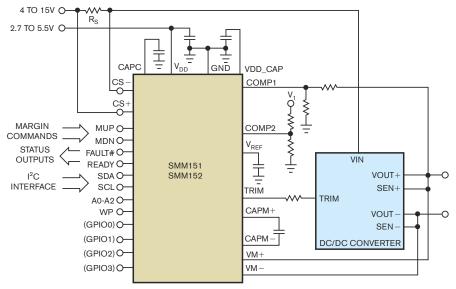

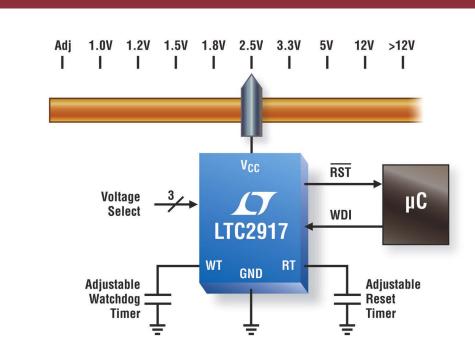

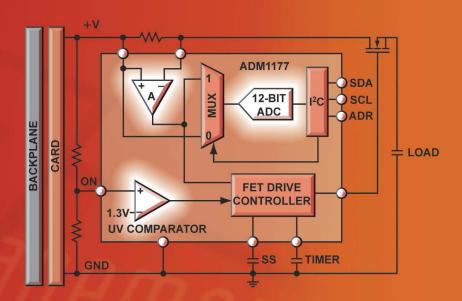

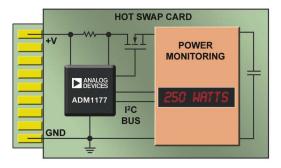

- 18 Power-supervision IC measures regulator-input current, differential-output voltage

- 18 Beagle Board opens embedded development

- 20 Integrated ORing controller and MOSFETs run fast and cool for redundant supplies

- 20 HDD (and SSD) capacities: up, up, and away

- 22 Voices: Pentek's Rodger Hosking: next-generation-radio architecture

## DEPARTMENTS & COLUMNS

- 10 EDN.comment: Oil prices, technology, and the cost of ignorance

- 24 Baker's Best: Transimpedance-amplifier stability is key

- 26 Prying Eyes: Prying apart a portable audio player

- 90 Tales from the Cube: The case of the stolen capacitor

## PRODUCT ROUNDUP

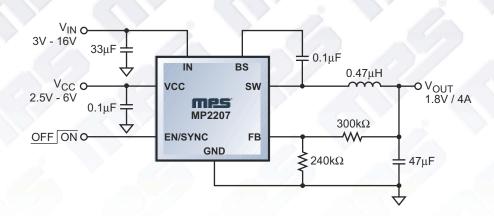

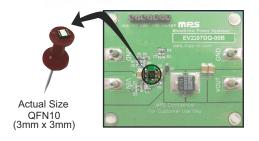

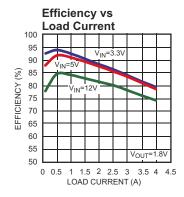

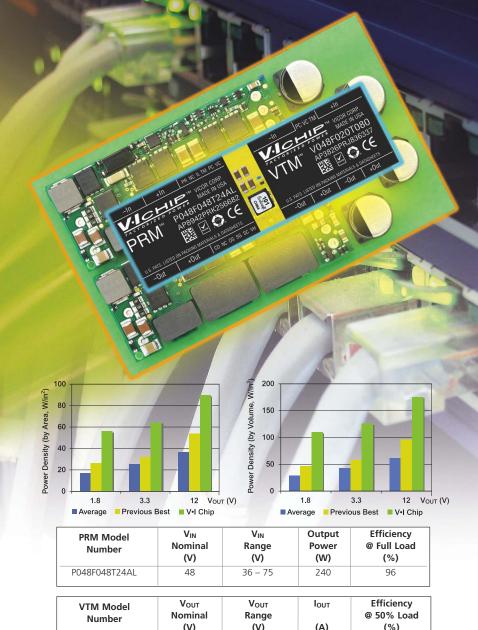

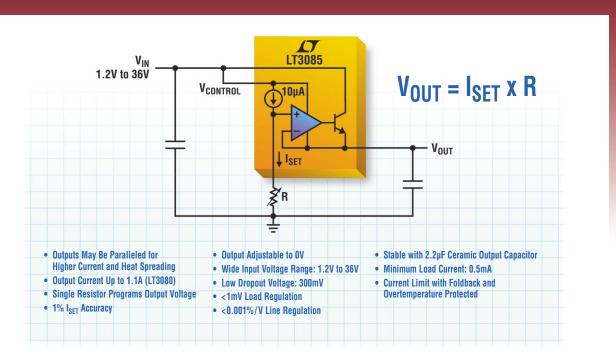

- 83 **Power Sources:** Switcher ICs, dc/dc converters, dual-output converters, dual low-dropout regulators, and pc-power-supply devices

- 87 Integrated Circuits: SOCs, 500-mA buck regulators, digital-media processors, and logic-gate optocouplers

- 88 Computers and Peripherals: 8-Gbyte storage devices, LCD monitors, handset-audio filtering devices, Mac memory kits, and more

EDN® (ISSN#0012-7515), (GST#123397457) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blwd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer; Mark Finkelstein, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintainian dat Reed Business Information, 8878 S Barrons Blwd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 450-445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 450-445. POSTMASTER: Send address changes to EDN®, Send address changes to EDN®, Box 6315 one year, (Includes 7% GST, GST#123397457); Mexico, \$215 one year, air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blwd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 53, Number 18 (Printed in USA).

# The Newest Semiconductors

#### **New Products from:**

LEXAS

Authorized Distributor

INA333

Www.mouser.com/

tiamplifiers/a

STM32F103VET6

Microcontroller

www.mouser.com/st/a

WILCROCHIP

UNI/O™ Serial EEPROM

www.mouser.com/

microchip/a

#### The ONLY New Catalog Every 90 Days

Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 366 leading suppliers.

a tti company

The Newest Products

For Your Newest Designs

(800) 346-6873

## at edn.com

EXPANDED ENGINEERING COVERAGE PLUS DAILY NEWS, BLOGS, VIDEO, AND MORE.

#### ONLINE ONLY

Check out these Web-exclusive articles:

## High-voltage, low-noise converters: Jim Williams' prototype pictures

Longtime contributor Jim Williams, staff scientist at Linear Technology, went all out and built 10 prototype boards for a recent article on high-voltage, low-noise converters. Check out both the article and the boards here.

→www.edn.com/080904toc1

## Determining end-of-life, ESR, and lifetime calculations for electrolytic capacitors at higher temperatures

→ www.edn.com/article/CA6588368

## ESR calculations for electrolytic capacitors at lower temperatures

→www.edn.com/article/CA6588218

## Intel launches USB 3.0 extensible host-controller-interface draft spec

→www.edn.com/article/CA6587566

## ESL: the state of the industry and what's next

→www.edn.com/article/CA6588565

#### READERS' CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

## Photo-sensing circuits: The eyes of the electronic world are watching

Baker's Best: When exploiting the light sensitivity of silicon, the challenge lies in determining how to convert the low-level currents from the photo sensor into a useful electrical representation.

→www.edn.com/article/CA6582850

## MIT researchers use plant-energy-storage system for solar-storage innovation

→ www.edn.com/article/CA6583673

## Simple toggle circuits illustrate low power-MOSFET leakage

→www.edn.com/article/CA6582853

#### Virtualization and multicore x86 CPUs

→www.edn.com/article/CA6584878

## Magnetic measurement tools attract attention

→www.edn.com/article/CA6578134

## Intel, Samsung, TI, Toshiba maintain top spots in IC Insights semi ranking

→www.edn.com/article/CA6584172

#### THIS WEEK IN GEEK

EDNs Friday tech roundup, available in the Now Hear This blog.

→ www.edn.com/nowhearthis

## High Density and High Performance

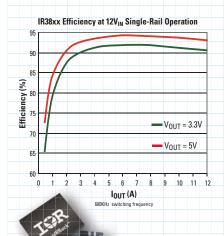

IR's Sup/RBuck™ Integrated Regulators deliver benchmark efficiency for data center and consumer applications

#### SupIRBuck Advantages:

- Integrates IR's high performance synchronous buck control ICs and benchmark HEXFET® trench technology MOSFETs

- 8-10% higher efficiency compared to monolithic Power IC two-stage solution

- High density compared to equivalent discrete solution

For more information call 1 800 981 8699 or visit us at www.irf.com/dcdc

#### BY RON WILSON, EXECUTIVE EDITOR

## Oil prices, technology, and the cost of ignorance

he world has just had a graphic demonstration of the workings of supply and demand in the oil industry. Supply of sweet, light crude became insufficient for the demand, and its price shot up. In response to the higher prices, demand for gasoline in the United States dropped, and the price shot back down again. In light of this dramatic performance, it is worth asking whether quick, technically feasible applications of

electronics could significantly reduce demand in the short term.

We are looking for feasible and fast solutions, so converting the entire Western world's vehicle fleet to fuel cells is out. So is covering two Southwestern states with photovoltaic cells or building a set of experimental but full-scale fusion reactors. Relatively quick measures do exist, however, and, unsurprisingly, they focus not on fundamental changes in society but on increasing efficiency.

One example dear to the hearts of many commuters is traffic control. In much of North America and, from the little we have seen, industrializing Asia, the entire notion that you can enhance rather than impede the flow of traffic by properly regulating traffic lights is an as-yet-unmade discovery. The cost of this ignorance is horrendous. Estimates show that a third of the fuels vehicles in urban areas consume go to waste because of unnecessary acceleration, almost entirely after a traffic control or jam has slowed the vehicle. Technologically simple computerized sensor and control networks and known algorithms could cut this waste by a large factor. The amount of necessary capital equipment and labor

Estimates show that a third of the fuels vehicles in urban areas consume go to waste because of unnecessary acceleration.

would be trivial in comparison with the savings and within the resources of even state-level governments without huge national subsidies. The only shortage is in the skill to install and operate the networks and the knowledge to recognize the problem.

Public transportation presents a similar example. Most municipalities in the world wear about their necks as a token of honor an ever-moving, constantly belching necklace of huge diesel buses, with a ratio of average payload weight to vehicle weight that would embarrass a Hummer owner. Municipalities could inexpensively replace most of these monstrosities with fuel-efficient small vans, directed by a network of GPS (global-position-system) sensors, traffic monitors, requester terminals, and computers,

creating an on-demand public-transit network that would function at a fraction of the fuel consumption and congestion generation of the behemoths. Again, there is no new technology here, and adequately suitable vehicles are currently languishing in automotive-dealer inventories.

Or consider where the demand for all that sweet, light crude oil comes from. The most dramatic increase isn't from sport-utility vehicles or corporate jets. It's from diesel generators because, in much of the developing world, local demand for electricity—partly created by our desire for cell phones and TV sets—is soaring. In countries that lack generation and distribution infrastructure, only local diesel generators can meet that demand. Hence, the demand for diesel soars—driving refineries to capacity and creating a shortage of sweet, light crude oil. (There is no shortage or price premium for high-sulfur crude, by the way. Few refineries can produce diesel from it.) So what would be the impact on demand if we focused our photovoltaic and storage efforts and subsidies not on wealthy North Americans' rooftops, but on developing-world towns and villages?

Many such opportunities exist to use a little understanding, a little technology, and a little capital to make a significant decrease in fuel consumption. And, as noted, a small decrease in consumption can make a big difference in global inflation pressure. But rest assured that these things will not happen. Inefficiency is one of the costs nature imposes as the price of public ignorance of technology. EDN

Contact me at ronald.wilson@reed business.com.

- + Go to www.edn.com/080904ed and click on Feedback Loop to post a comment on this column.

- + More at www.edn.com/edncomment

## More Q. Less Cu

## These tiny new air core inductors have the highest Q and current handling in the smallest footprint.

Coilcraft's new SQ air core inductors have unmatched Q factors: most are above 200 in the 1-2 GHz range! That's 3 times higher than comparably sized 0805 chip coils.

And with their extremely low DCR, they can handle 4 to 8 times more current: up to 4.4 Arms.

SQ air core inductors are perfect for your LC filter and RF impedance matching applications. They come in 15 values ranging from 6 to 27.3 nH, all with 5% tolerance.

These coils

are significantly smaller than existing air core inductors. We reduced the footprint by using close-wound construction and keeping the leads close to the body. The square shape cuts the height to as low as 1.5 mm and creates flat top and bottom sur-

Q factors are 3X higher than

standard chip inductors

The square shape and narrow footprint reduce board space by 60-75% over conventional air core inductors.

faces for easy automated handling and stable mounting.

See how the ultra-high Q and current handling of Coilcraft's new SQ air core inductors can maximize the performance of

your next design. For complete specifications and free evaluation samples, visit www.coilcraft.com/sq

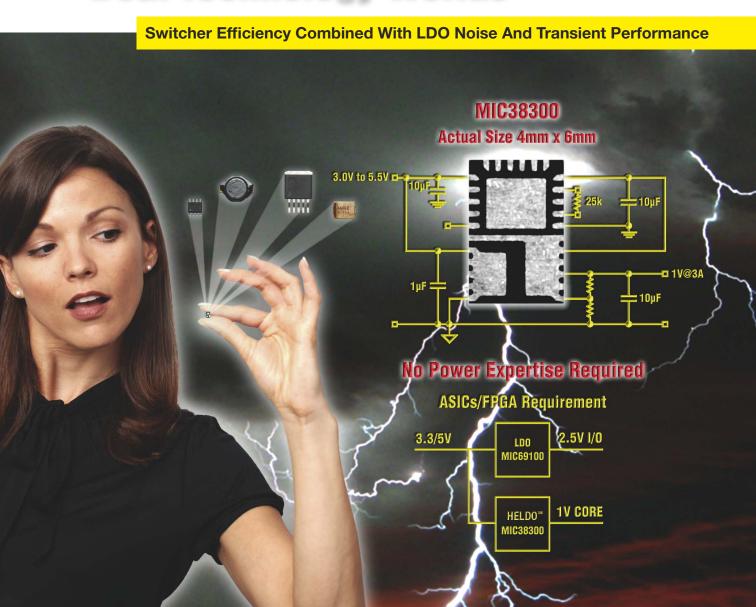

## Power That Gives You The Best Of Both Technology Worlds

The MIC38300 is a 3A step down converter and the first device in a new generation of HELDO™ products providing the benefits of LDOs with respect to ease of use, fast transient performance, high PSRR and low noise while offering the efficiency of a switching regulator.

As output voltages move lower, the output noise and transient response of a switching regulator become an increasing challenge for designers. By combining a switcher whose output is slaved to the input of a high performance LDO, high efficiency is achieved with a clean low-noise output.

For more information, contact your local Micrel sales representative or visit us at: www.micrel.com/ad/mic38300.

#### The Good Stuff:

- 2.2A Continuous operating current

- ◆ Input voltage range: 3.0V to 5.5V

- ◆ Adjustable output voltage down to 1.0V

- ◆ Output noise less than 5mV

- ◆ Ultra fast transient performance

- ◆ Unique Switcher plus LDO architecture

- ◆ Fully integrated MOSFET switches

- Micro-power shutdown

- ◆ Easy upgrade from LDO as power dissipation becomes an issue

- ◆ Thermal shutdown and current limit protection

- ◆ 4mm × 6mm × 0.9mm MLF ® package

#### PRESIDENT, BOSTON DIVISION, REED BUSINESS INFORMATION

Mark Finkelstein, mark.finkelstein@reedbusiness.com

1-781-734-8431

#### PUBLISHER, EDN WORLDWIDE

Russell E Pratt, 1-781-734-8417; rpratt@reedbusiness.com

#### ASSOCIATE PUBLISHER. EDN WORLDWIDE

Judy Hayes, 1-408-345-4437; judy.hayes@reedbusiness.com

#### VICE PRESIDENT, EDITORIAL DIRECTOR

Karen Field, 1-781-734-8188; kfield@reedbusiness.com

#### EDITOR-IN-CHIEF. EDN WORLDWIDE

Rick Nelson, 1-781-734-8418; rnelson@reedbusiness.com

#### **EXECUTIVE EDITOR**

Ron Wilson, 1-408-345-4427; ronald wilson@reedbusiness.com

#### MANAGING EDITOR

Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com Contact for contributed technical articles

#### EDITOR-IN-CHIEF, EDN.COM

Matthew Miller

1-781-734-8446; fax: 1-303-265-3017; mdmiller@reedbusiness.com

#### SENIOR ART DIRECTOR

Mike O'Leary

1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

#### **EMBEDDED SYSTEMS**

Warren Webb, Technical Editor 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

#### MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-760-0159: fax: 1-303-265-3187: bdipert@edn.com

#### MICROPROCESSORS, DSPs, AND TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

#### NEWS

Suzanne Deffree, Managing Editor 1-631-266-3433: sdeffree@reedbusiness.com

#### POWER SOURCES. ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

#### SEMICONDUCTOR MANUFACTURING AND DESIGN

Ann Stefforg Mutschler, Senior Editor 1-408-345-4436: ann.mutschler@reedbusiness.com

#### **DESIGN IDEAS EDITOR**

Martin Rowe

edndesignideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439; fax: 1-303-265-3131: f.granville@reedbusiness.com

#### ASSOCIATE EDITOR

Maura Hadro Butler, 1-617-276-6523;

mbutler@reedbusiness.com EDITORIAL/WEB PRODUCTION

Diane Malone, Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442; fax: 1-303-265-3198 Melissa Annand, Newsletter/Editorial Coordinator 1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager

1-781-734-8325; fax: 1-303-265-3042

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

## Reed Electronics Group

#### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn: Pallab Chatteriee

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329

Kelly Jones, Production Manager 1-781-734-8328; fax: 1-303-265-3164 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-303-265-3015

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

#### EDN ASIA

Susie Newham, Managing Director susie.newham@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

#### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.ip Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

#### **DENNIS BROPHY**

Director of Business Development, Mentor Graphics

#### DANIS CARTER

Principal Engineer, Tyco Healthcare

#### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne

#### DMITRII LOUKIANOV

System Architect, Intel

#### RON MANCINI

Retired Staff Scientist

#### GABRIEL PATULEA

Design Engineer, Cisco

#### DAVE ROBERTSON

Product Line Director, Analog Devices

#### SCOTT SMYERS

VP Network and System Architecture Division, Sony

#### TOM SZOLYGA

Program Manager, Hewlett-Packard

#### JIM WILLIAMS

Staff Scientist, Linear Technology

## **Simplify Switch System** Management

#### **NI Switch Executive**

Accelerate development and simplify maintenance of your switch system

- Intuitive graphical utility for rapid channel and route configuration

- Interactive channel routing

- Validation, simulation, and reporting tools

- Easy integration with NI LabVIEW and NI TestStand

>> Learn more at ni.com/switchexecutive

800 891 8841

©2008 National Instruments. All rights reserved. LabVIEW, National Instruments, NI, ni.com, and NI TestStand are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. 2008-9806-101-D

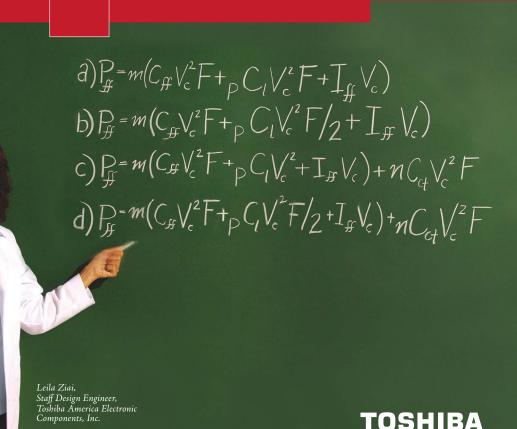

## "Sweating the details" redefined by Toshiba.

Toshiba sweats every detail in order to deliver expert, responsive technical service/support for its electronic components. The Toshiba design centers have a team of engineers dedicated to power analysis to ensure optimum power management. Toshiba Virtual Prototyping—our exclusive system for chip/package/system co-design for Custom SoCs—delivers a power-optimized model usually in less than eight weeks. And we employ advanced

TOSHIBA

low-power design techniques like Multi-Vth, Clock Gating and much more. This commitment to delivering unmatched technical expertise is our formula for customer success.

Which equation below is the most accurate estimate for power consumed by flip flops on a chip? Use the legend at transform.toshiba.com to solve the equation and win a hoody sweat shirt (while supplies last).

Leading Innovation >>>

### Video, graphics module drives dual displays

ith advanced-sensor-fusion, imagemanipulation, and tactical-movingmap applications in mind, Aitech Defense Systems recently introduced the M590 graphics and video PMC (peripheralcomponent-interconnect-mezzanine-card) module that simultaneously outputs information from two independent data streams to two analog or digital displays. The new M590 supports 2- or 3-D-video displays plus image capture with overlay and underlay features to provide man-machine interfaces with resolutions as high as 1536×2048 pixels at 30- to 200-Hz refresh rates and as many as 32 bits per pixel.

An AMD ATI (www.amd.com) M9 graphics processor with an on-chip 64-Mbyte frame-buffer array and dual RAMDAC (random-access-memory-digital-to-analog-converter) units power the M590, which performs high-speed 2-D-line, 3-D-polygon, and texture acceleration. The module also supports multiple video-input and -output formats, including NTSC (National Television System Committee) and PAL (phase-alternating line) for both interlaced and noninterlaced monitors. For advanced video-display applications,

Aitech's new PMC drives dual 2- or 3-D-video displays from independent data streams at resolutions as high as 1536×2048 pixels.

the M590 provides video overlay and underlay functions that generate images, superimpose an input from one of the various video formats, and drive the result to a monitor. The module's software package supports all onboard capabilities and features OpenGL drivers for both VxWorks and Integrity real-time operating systems. The M590 is available in commercial-, rugged-, and military-temperature ranges and in either conduction- or air-cooled versions. The price for an M590 starts at \$3440 (OEM quantities).-by Warren Webb

>Aitech Defense Systems Inc. www. rugged.com.

#### FEEDBACK LOOP

"A young graduate I once worked with told me he got into engineering for one reason to learn a bit about engineering so that he could go back to school to get a law degree and get rich by suing big corporations over engineering patents."

-Reader and frequent EDN contributor Glen Chenier, in EDN's Feedback Loop, at www. edn.com/article/CA6578140. Add your comments.

#### AMD updates Stream software-development kit

To help increase the ease and efficiency of software development using its Stream-processing approach, microprocessor challenger AMD (Advanced Micro Devices) recently announced an extensive set of upgrades for future versions of the Stream softwaredevelopment kit. AMD intends that these upgrades will reduce the time and effort required to produce GPU (graphics-processing-unit)-accelerated applications that run on multiple platforms, with expanding support for industry-standard APIs (applicationprogramming interfaces) and enhanced support for C/C++. The updates will add full support for DirectX 11, the next-generation suite of advanced APIs from Microsoft (www.microsoft.com).

DirectX 11 builds on the performance of DirectX 10.1 for 3-Dgraphics rendering and gaming control and includes new technologies to ease the creation of general-purpose graphics-processing-accelerated applications that can run on any Windows Vistapowered platform. AMD is supporting efforts to develop OpenCL as an open standard and plans to evolve the Stream softwaredevelopment kit to comply with OpenCL. The company is continuing to give developers the option of creating and using their own programming languages and high-level tools.

-by Ann Steffora Mutschler

▶Advanced Micro Devices Inc. www.amd.com.

### Touch-panel controller targets media-device interfaces

tmel, in the form of its recently acquired subsidiary, Quantum Research Group, has introduced a touch controller that combines a slider control with buttons, an integrated LED controller, and GPIO (generalpurpose-input/output) functions. The AT42QT2160, part of the company's new QTouch series, uses charge-transfer technology to control as many as 16 touch keys with a slider that you can configure to use two to eight of the touch-key channels. If you need an extra-long slider control, you can add interpolation between points with a resistive-touchsensor element.

The chip can also control as many as 11 LEDs through a host-controlled PWM-output function, eliminating the need for an external LED controller.

Atmel designed the device for use as a multimedia-HMI (human-machine-interface) controller in mobile phones and consumer electronics, such as personal media players. It operates from 1.8 to 5.5V, and you can also use it in applications such as digital still cameras, PDAs (personal digital assistants), and handheld gaming devices. Like previous chips using the charge-transfer technology, the 2160 claims high immunity to EMI (electromagnetic interference) through spread-spectrum modulation and filtering algorithms, calibration of the device over its lifetime, and designer-defined sensitivity thresholds for individual keys. AKS (adjacent-key

suppression) intelligently suppresses signals from nearby keys so that only the keys that a user intends to touch register a touch.

The AT42QT2160 has three GPIOs with PWM capability and eight shared-output ports that provide additional standard outputs for the host without adding cost or using an extra I/O-expansion device. You configure the device with an I2C (inter-integrated-circuit) interface. You might design touch-buttonsensor electrodes of any arbitrary size greater than 6×6 mm and of arbitrary shape, as copper pads on the PCB (printedcircuit board) or a flexible circuit. The chip senses touches to those pads through glass or plastic as thick as 2.5 mm.

Samples of the AT42QT-2160 are available now in a 28-pin, 4×4-mm QFN package; it sells for 98 cents (10,000). An evaluation board, which comes with an I2C-to-USB converter to connect to a PC, costs \$82.50.

-by Graham Prophet >Atmel, www.atmel.com.

Atmel's QTouch controller integrates enough functions to control a complete media device.

#### **DILBERT By Scott Adams**

SYSTEM DESIGN **Building on its popular** FPGA-based PXI (PCI extensions for instrumentation), PC, and Compact-RIO (reconfigurable-input/output) platforms, National Instruments has announced a new line of single-board RIO modules that offers a lower-cost, integrated-hardware option for embedded control and data-acquisition applications. The RIO-96xx devices combine a real-time embedded processor, a reconfigurable FPGA, and analog and digital I/O on an 8.2imes5.6in. PCB (printed-circuit board). Designers can use the company's Lab-View software to configure the RIO hardware and the application's embedded firmware.

**MODULE TARGETS EMBEDDED**

The modules feature a 266- or 400-MHz Freescale (www.freescale. com) MPC5200 processor, the Wind River (www. windriver.com) VxWorks real-time operating system, and a Xilinx (www. xilinx.com) Spartan-3 FPGA. The onboard analog and digital I/O connects to the FPGA to provide low-level customization of timing- and I/Osignal processing. You can expand the I/O capabilities using three expansion slots for custom hardware or any C-Series I/O module. Prices for the devices start at \$1000 (100 or more). Watch a demonstration video at www.ni.com/singleboard. -by Warren Webb

National Instruments, www.ni.com.

© Agilent Technologies, Inc. 2008

Agilent 34970A & 34980A switch/measure units

### More measurements. More data. Less cost.

With up to 560 channels of data logging at a maximum scan rate of 1000 channels/sec, an internal 6  $\frac{1}{2}$  digit DMM with 22-bit resolution, and 0.03% accuracy, it's no mystery why Agilent's data acquisition systems are among the top selling in the world. The 34970A and 34980A are both at home with either data acquisition or functional test, with a broad selection of plug-in modules.

Now with Agilent Data Logger Pro software, you'll be able to collect data, check limits, perform extensive branching, and view and store the data without authoring the programming yourself. It's an ideal expansion at a significant savings.

FREE Agilent Data Logger Pro software a \$795 - \$995 value until 15 Oct 2008

u.s. 1-800-829-4444 canada 1-877-894-4414 www.agilent.com/find/daqpromo

Agilent Authorized Distributor

866-436-0887 www.metrictest.com/agilent

### Power-supervision IC measures regulator-input current, differential-output voltage

ummit Microelectronics' new SMM151 powersupervision IC allows digital control and monitoring of any voltage regulator. The device monitors input current to the target regulator so there is no added impedance to the output rail. A differential pair that can accept 15V inputs performs the voltage sensing, which is accurate to  $\pm 1\%$ ; current-sensing accuracy is ±2%.

The part operates from 2.7 to 5.5V of power and has an I<sup>2</sup>C (inter-integrated-circuit) interface that allows system monitoring in real time with parameters that you can change using the I2C bus. The unit provides fault- and ready-status outputs and accepts margin commands on two dedicated pins or the I<sup>2</sup>C bus.

The IC allows users to program limits for glitch-filter duration, margin delays, and response to fault conditions. A sister part, the SMM152, also has four general-purpose I/O pins. Developers can program the power-on state of these pins and store that information

in nonvolatile memory within the IC. All family members have two comparators for detecting levels or providing window comparisons, and they target applications in computing and datacom equipment, servers, wireless routers, and other high-reliability systems.

The SMM151EV evaluation board works through a USB port with Summit's Windowsbased GUI (graphical user interface), which allows designers to set up the operating parameters and then program them into nonvolatile memory. Once designers define the device's functions, they can extract a hex file from the evaluation board that allows Summit to provide the part in volume quantities.

The device operates in a 0 to 70 or a -40 to  $+85^{\circ}$ C temperature range and comes in a  $5\times5$ -mm, 28-pad QFN package. The SMM151 and SMM152 sell for \$3.49 and \$3.79 (1000), respectively. Samples and the SMM151EV evaluation modules are available, and volume production has begun.-by Paul Rako

Summit Microelectronics. www.summitmicro.

com/SMM151.

The SMM151 power-supervisor IC provides voltage and current measurement as well as margining and supervisory functions.

#### EMBEDDED WEBBLOG

## Beagle Board opens embedded development

OFFERING DESIGNERS and hobbyists a low-cost starting point for device development, Digi-Key, Texas Instruments, and a group of volunteers have joined forces to create an open, single-boardcomputer design that can be adapted to a multitude of embedded projects. The module, dubbed the Beagle Board, is a low-power, fanless design incorporating TI's recently

introduced OMAP35x processors based on the ARM Cortex-A8 core.

The design reduces cost and power requirements by eliminating most onboard peripherals, except those provided by the processor, and incorporating standard expansion buses, like high-speed USB 2.0 and SDIO for application-specific I/O. The processor contains

2-D- and 3-D-graphics acceleration capabilities plus a DSP optimized for multimedia processing.

Further simplifying development, the board is completely powered by the onboard USB interface used for downloading the software from a laptop or desktop computer. The open-source-software-development community provides a Linux operating

system specifically configured for the Beagle Board.

A 132-pg hardware-reference manual is available for download at the Beagle-Board.org Web site and provides complete module component descriptions, schematics, and board-manufacturing documentation.

#### -by Warren Webb

- ▶www.edn.com/webblog.

- ▶For the full post, go to www. edn.com/080904b1.

are both available in the 8-pin DC package and the dual-redundant 16-pin GO package.

For more information call (603) 223-2362 or visit our website: www.melexis.com

## Integrated ORing controller and MOSFETs run fast and cool for redundant supplies

n their quest for near-100% uptime, designers of highavailability-system applications, such as telecom and datacom servers, employ redundant-power systems: If one power supply fails, a redundant supply can pick up the load. Redundant- and backuppower supplies enter the load along with ORing MOSFETs, which ideally should have a minimal on-state resistance and fast dynamic response to power source failures.

Picor's Cool-ORing family, comprising the PI2121, PI2123, and PI2125 devices, integrates high-speed ORing-MOSFET controllers with lowon-state-resistance MOSFETs that typically achieve a dynamic response within 160 nsec. The 8V, 24A PI2121 targets use in applications with bus voltages of 5V or lower; the 15V, 15A PI2123 suits applications with bus voltages of 9.6V or lower; and the 30V, 12A PI2125 suits applications with bus voltages of 12V. The typical on-state resistances for the three parts are 1.5, 3, and 5.5 m $\Omega$ , respectively. Each part can also work in parallel to address higher current requirements through a master/slave feature. The devices detect normal-forward, excessive-forward, light-load, and reverse-current flow through their internal MOSFETs, and they report fault conditions through an active low-faultflag output. A temperaturesensing function indicates a fault if the maximum junction temperature exceeds 160°C. You can program the undervoltage and overvoltage

Picor's Cool-ORing family of devices integrates high-speed ORing-MOSFET controllers with low-on-state-resistance MOSFETs that achieve a typical dynamic response of 160 nsec and a typical on-state resistance as low as 1.5 m $\Omega$ .

thresholds using external resistor dividers.

The family also includes discrete versions of the ORing controllers. The high-speed, active-ORing PI2001 controller targets use with industrystandard single or paralleled MOSFETs; the PI2003 controller suits use in -48V, redundant-power architectures and systems requiring operation during input-voltage transients as high as 100V for 100 msec; and the high-speed, active-ORing P12002 controller IC has a load-disconnect feature that functions like that of the PI2122 but works with industry-standard, back-to-back N-channel MOSFETs.

The Pl2121, Pl2123, and PI2125 come in 17-pin,  $5\times$ 7×2-mm-high, thermally enhanced LGA packages and sell for \$1.98 (10,000). The discrete Cool-ORing controllers are available in 3×3-mm, 10lead TDFN packages and sell for 84 cents for the PI2001 and PI2003 and 92 cents (10.000) for the PI2002. An eight-lead SOIC-package option costs 76 cents for the PI2001 and PI2003 and 83 cents for the PI2002 (10,000).

-by Margery Conner ▶ Picor, www.vicorpower.com/ picorpower.

#### **BRIAN'S BRAIN**

## HDD (and SSD) capacities: up, up, and away

IT SEEMS LIKE just yesterday that I was first writing to you about the world's first 1-Tbyte, 3.5-in. HDD (hard-disk

drive). Hitachi's accomplishment didn't remain sole-sourced long, of course, given the hypercompetitiveness of the HDD industry. Seagate

launched a four-platter (250-Gbyte/platter) configuration in June 2007, along with a Samsung paper launch of a three-platter (333-Gbyte/ platter) configuration in that same time frame. Western Digital waited until late July 2007 to unveil its own fourplatter configuration, and recent data suggests that

Samsung's products are finally shipping in volume (as well that 1-Tbyte drives have dipped below \$150!).

> Recent announcements show that vendors' competitive juices have by no means abated, even in the slightest. On July 9,

Hitachi finally got its 1-Tbyte drive down to a three-platter configuration, the 7200-rpm Deskstar 7K1000.B. One day later, Samsung released the world's first 1.5-Tbyte HDD, high-end member of the 7200.11 product family, which was scheduled to enter production in August. At 375 Gbytes/platter, it hits a new

**CG** Hitachi's accomplishment didn't remain solesourced long, of course.

bit-packing peak for PMR (perpendicular-magneticrecording) technology. That same generation of magnetic recording translates to 0.5-Gbyte, 5400- and 7200-rpm, 2.5-in. HDDs, which won't appear until some time in the fourth quarter.

And what about the SSD (solid-state-drive) alterna-

tive? Although SSDs lag their HDD counterparts on both absolute capacity and cost/ gigabyte metrics, suppliers continue striving to at least maintain pace with the rotating-storage mainstay. Witness, for example, Samsung's 128-Gbyte SSD announcement. Samsung accomplishes this 2.5-in.-form-factor feat by means of MLC (multilevelcell, also known as 2-bit-percell) NAND-flash memory, which roughly doubles the amount of storage capacity achievable for a given amount of silicon area on a given process lithography.

#### -by Brian Dipert

- www.edn.com/briansbrain.

- ▶For the full post, go to www. edn.com/080904b2.

#### **Our newest Advantiv innovations**

#### Audio Processor for Advanced TV: ADAV4622

High-fidelity uninterrupted sound; supports multiple audio standards; simplifies designs for shorter time to market.

#### Class-D Stereo Power Stage: ADAU1513

Complete audio amplifier section; pop-and-click-free audio; promotes seamless interconnectivity.

#### Video Decoder with 3D Comb Filter: ADV7802

High quality images from composite input; vivid color; improves quality of VCR tapes shown on HDTVs.

## **Low Power HDMI Transmitter with CEC: ADV7520NK**Longer battery life; lighter and smaller designs; enables

single remote for camcorder and TV control.

#### HDMI/DVI 1:1 Buffer: AD8195

Features equalized TMDS inputs and pre-emphasized TMDS outputs; insures HDMI compliance on systems with long cable runs.

analog is everywhere:

## For HD audio, video, and interconnectivity that excites and delights, put ADI's Advantiv™ portfolio into action

Crystal clear video. Rich, true-to-life sound. Deep color quality. And superior plug 'n play functionality. Those are just a few of the joys of using the latest HDTVs, DVD players, DVRs, AVRs, camcorders, and set-top boxes that are built with Analog Devices' technology inside. In virtually every aspect of HD delivery, designers who select from the Advantiv portfolio are benefiting from ADI's audio and video signal processing expertise.

For more than 40 years, ADI has led with technology and support tailored to meet the demands of the toughest applications. Wherever user experience defines the design, Analog Devices defines the possibilities.

To experience what Analog Devices can do for your design, call 1-800-AnalogD or visit www.analog.com/Advantiv-1.

## **VOICES**

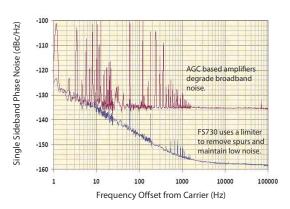

## Pentek's Rodger Hosking: next-generation-radio architect

odger Hosking is vice president and co-founder of Pentek Inc, where he is responsible for new-product definition, technology development, and strategic alliances. With more than 30 years' experience in the electronics industry, he has authored hundreds of articles about software radio and digital-signal processing. He designed the first commercial direct-digital-frequency synthesizer and holds patents in frequency synthesis and FFT (fast-Fourier-transform)-spectrumanalysis techniques. Hosking has a bachelor's degree in physics from Allegheny College (Meadville, PA) and both bachelor's and master's degrees in electrical engineering from Columbia University (New York).

What are the technical challenges that you face in highperformance-data-acquisition- and software-radioproduct development?

Complexity of the silicon devices, coupled with high component density and power dissipation, pushes the limits of PCB [printed-circuit-board] design, mechanical packaging, and thermal-management technology. Gigabit serial links impose strict layout rules for matching lengths and impedances of differential-signal pairs. Testing and validation of new designs requires not only hardware expertise, but also a significant software effort because of the complexity and inaccessibility of hardware test points. Drivers and software libraries offered by the COTS [commercial-off-the-shelf] vendors to support customer-development efforts need to support multiple operating-system environments and require more testing, qualification, and documentation than ever before.

All of these factors lead to longer development cycles while the rate of new-technology-device introductions is increasing. This [combination of factors] leads to shorter life cycles for each product, even though development costs are higher.

As you look ahead for the next few years, which technologies and applications present the most interesting opportunities?

FPGAs have created a major shift in COTSproduct offerings for data acquisition and software radio by offering critical functions, including fast and flexible I/O resources, DSP engines, configurable logic and RAM, gigabit serial interfaces, and builtin microcontrollers. All of these features will become more powerful in next-generation FPGAs. Monolithic ADC and DAC technology will continue to advance both resolution and sampling rates while tam-

ing power dissipation with new silicon techniques.

These trends will support small, complete, system-level solutions close to the antennas and sensors. They will include acquisition, generation, upconversion and downconversion, modulation and demodulation, analysis and detection, buffering and forwarding, and local supervisory and decisionmaking functions. High-speed gigabit links will connect these autonomous subsystems to a central facility through dedicated paths or over the Internet.

As a COTS-board manufacturer, how do you prevent the interoperability issues when designing for today's rival fabric-interconnection standards?

The most successful tactic has been to follow the standards as closely as possible and declare each level of compliance your product supports. A series of simple example programs demonstrating operation of the basic messaging types can be extremely useful for interfacing with products from other vendors.

Which engineering talents are most important to Pentek, and how do you find and retain them?

Fifteen years ago, we had one software engineer for every three hardware engineers. That ratio is now exactly reversed due to

the complexity of the products and the need to provide higher-level tools to our customers. Our most capable FP-GA designers started as hardware engineers with a flair for algorithms, DSP, and software tools. More than ever, technical writers need to be capable engineers with specific expertise in the area of technology they are documenting but not so close to it that they overlook the need to explain some of the basics in our manuals. Customer-support engineers need a special blend of technical expertise, patience, and empathy to help customers become successful, even if it is their first exposure to this complex technology.

Retaining engineers is difficult because each one is uniquely qualified and motivated, but tasking them with several areas of engineering responsibilities often proves to be a successful strategy.

What motivated you to select electrical engineering and the high-tech industry as a profession?

As a very small child, I was always fascinated with anything that had to do with electricity. Later on, I became an avid electronics hobbyist, building hundreds of my own projects inspired by magazine articles and books. For me, a career in electronics was a no-brainer.

What activities do you pursue for relaxation outside your high-tech work environment?

Outside work, I spend my time running, rollerblading, ballroom dancing, watching old movies, and listening to music from the '30s and '40s.

-Interview conducted and edited by Warren Webb

## **Rarely Asked Questions**

Strange stories from the call logs of Analog Devices

## Lock Down That Noise — Don't Let It Escape

**Q.** How can I prevent switching-mode power supply noise from devastating my circuit performance?

**A.** With great difficulty — but it can be done.

Switching-mode power supplies are inherently the noisiest circuits imaginable. A large current from the supply is being turned on and off at high frequency with very fast dl/dt. There are inevitably large fast voltage and current transients.

The only way to prevent interference to sensitive circuitry in the system is to keep the transients within the converter. We cannot stop switching large currents inside it, but we can, and must, prevent the transient currents and voltages from escaping. Start by grounding all the terminals of the converter at AC.

Capacitors block DC but have low impedance at AC, so they should be ideal for this purpose. In theory, if we place a large capacitor between the converter input and its ground, the input will keep the capacitor charged and the transient currents will flow in the capacitor and not from the power source. A similar output capacitor absorbs transients and sources steady DC.

Unfortunately when we actually build such a system it is common to find much more noise than we can tolerate in the input and output circuits - what can be wrong?

If the capacitor is placed some distance from the converter, the impedance, resistive and inductive, of its connection to the converter will be large enough to prevent it from working properly; if it is chosen badly it will have higher impedance

than the basic  $1/2\pi fC$  formula predicts; and if it shares its ground path with other circuitry the noise in the common ground impedance will be disruptive.

Add to these effects the less important, but still damaging, consequences of external currents induced by fast-changing magnetic and electrostatic fields, and even electromagnetic radiation, from within the converter, and it is obvious that preventing converter noise is not simply a matter of placing a couple of random capacitors on its input and output.

Silencing a DC-DC converter requires systematically finding all the possible paths by which noise can escape from it, and ensuring that they are all locked down. The linked article discusses how this may be done.

Of course before we start we must choose or design the converter itself to have minimal external noise. This is a separate issue which may be discussed in a future RAQ.

> To Learn More About Power Supply Noise

Go to: http://rbi.ims.ca/5721-101

Contributing Writer

James Bryant has been

a European Applications Manager with

Analog Devices since

1982. He holds a degree

in Physics and Philosophy from the University of Leeds. He is also

C.Eng., Eur.Eng., MIEE,

and an FBIS. In addition to his passion for

engineering, James is

a radio ham and holds

the call sign G4CLF.

Have a question involving a perplexing or unusual analog problem? Submit your question to: raq@reedbusiness.com

For Analog Devices' Technical Support, Call 800-AnalogD

SPONSORED BY

#### BY BONNIE BAKER

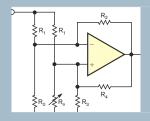

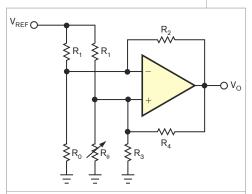

## Transimpedance-amplifier stability is key

variety of precision applications sense light and convert that information into a useful digital word. At the system's front end, a preamplifier converts the photodiode's current-output signal to a usable voltage level. Figure 1 shows the front-end circuit of this system, which comprises a photodiode, an operational amplifier, and a feedback network. The transfer function of this system is:

$$V_{OUT} = \frac{I_{SC} \times R_F}{1 + 1/(A_{OL}(j\omega) \times \beta)},$$

where  $A_{OL}(j\omega)$  is the open-loop gain of the amplifier over frequency;  $\beta$  is the system-feedback factor, equaling  $1/(1+Z_{IN}/Z_F)$ ;  $Z_{IN}$  is the distributed input impedance, equaling  $R_{PD} \parallel j\omega(C_{PD} + C_{CM} + C_{DIFF});$  and  $Z_{F}$ is the distributed feedback impedance, equaling  $R_F \parallel j\omega(C_{RF} + C_F)$ .

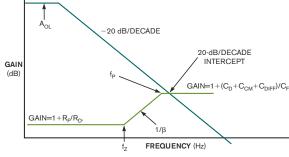

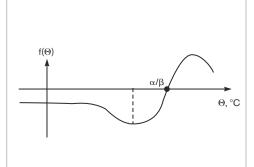

A good tool for determining stability is a Bode plot. The appropriate Bode plot for this design includes the amplifier's open-loop gain and the  $1/\beta$ curve. System elements determining the noise-gain frequency response are amplifier's feedback loop. Figure 2 shows the frequency response of the  $1/\beta$  curve and the amplifier's open-loop-gain response:  $f_p = 1/$  $(2\pi(R_{PD} || R_F)(C_{PD} + C_{CM} + C_{DIFF} + C_F +$  $C_{RF}$ ), and  $f_7 = 1/(2\pi(R_F)(C_F + C_{RF}))$ . The  $A_{OI}(j\omega)$  curve intersects the  $1/\beta$ curve at an interesting point. The

the photodiode's parasitics and the operational amplifier's input capaci-

tance, as well as  $R_F$ ,  $C_{RF}$ , and  $C_F$  in the

closure rate between the two curves suggests the system's phase margin and, in turn, predicts the stability. For instance, the closure rate of the two curves is 20 dB/decade. Here, the amplifier contributes an approxi-

> mately  $-90^{\circ}$  phase shift, and the feedback factor contributes an approximately 0° phase shift. By adding the  $1/\beta$  phase shift from the  $A_{OI}(j\omega)$ phase shift, the system's phase shift is  $-90^{\circ}$ , and its margin is 90°, resulting in a stable system. If the closure rate of these two curves is 40 dB/decade, indicating a phase shift of  $-180^{\circ}$  and a phase margin of 0°, the

Figure 1 This transimpedance photosensing circuit comprises a photodiode, an operational amplifier, and a feedback network.

circuit will oscillate or ring with a

step-function input.

One way to correct circuit instability is to add a feedback capacitor, C<sub>F</sub>, or to change the amplifier to have a different frequency response or different input capacitance. A conservative calculation that allows

variation in amplifier bandwidth, input capacitance, and feedback-resistor value places the system's pole of  $1/\beta$ at half the frequency where the two

$$C_{F} = \left[2 \times \sqrt{\frac{(C_{PD} + C_{CM} + C_{DIFF})}{2\pi R_{F} f_{GBW}}}\right] - C_{RF},$$

where  $f_{GBW}$  is the gain-bandwidth product of the amplifier. In this design, the system's phase margin is 65°, and the step function's overshoot is 5%.EDN

#### REFERENCE

■ Baker, Bonnie, "The eyes of the electronic world are watching," EDN, Aug 7, 2008, pg 24, www.edn.com/ article/CA6582850.

Bonnie Baker is a senior applications engineer at Texas Instruments and author of A Baker's Dozen: Real Analog Solutions for Digital Designers. You can reach her at bonnie@ti.com.

Figure 2 The closure rate between the open-loop-gain frequency response and the feedback-gain response is 20 dB/decade.

## Design with the best: High Performance Analog

## Design with the best brands

You'll find the best components and the best information in one site. Visit www.newark.com/instrumentation to make the most of the newest advances in high performance processing, high performance analog, power supplies, imaging, connectors, discretes and passives.

Find more at www.newark.com and 1.800.4.NEWARK

Tiny package creates space by mounting on back of board.

#### PRY FURTHER AT EDN.COM

+ Go to www.edn.com/080904pry for an expanded version of this

## Prying apart a portable audio player

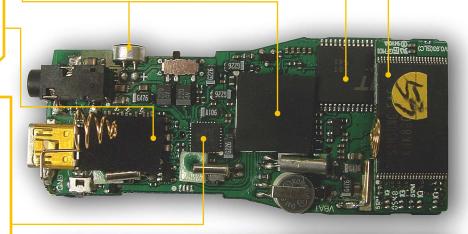

ree after \$65 rebate with free shipping. That's the deal that routed a refurbished Sandisk Sansa M250 from Newegg to my front door last summer. I suspected it would make a fine Prying Eyes patient, and, as it turns out, I was right. Let's see what's inside, shall we?

The system's "brains" consist of an ARM9-based and USB2-support-inclusive Telechips TCC770. The Sansa M250's built-in microphone for voice recording and subsequent playback likely harnesses the CPU's ADPCM (adaptive-differential-pulsecode-modulation)-audio-codec support.

Texas Instruments' TLV320AIC-23B two-channel codec-that is, ADC and DAC-with headphone amplifier is another notable IC in this design; however, the player doesn't fully harness the chip's 24-bit maximum per-channel sample size and 96-kHz peak sample rate.

The Sansa M250 uses the Philips (now NXP Semiconductors) TEA5767HN FM radio IC for playback only-that is, the Sandisk unit offers no support for live recording and later listening. The lack of a discrete antenna embedded within the Sansa M250's plastic case probably indicates the use of the headphone wire for this function.

The Telechips TCC770 advertises limited-codec image-decoding support: JPEG pictures and MPEG-4 Simple Profile video clips. The Sansa M250 collateral makes no mention of image-file capabilities; then again, the unit's 128×64-pixel monochrome LCD wouldn't really do them justice, anyway.

The Sansa M250 embeds a single battery-backed, 16-Mbit Elite Semiconductor M12S16161A SDRAM, supplementing the 64 kbytes of SRAM within the Telechips TCC770. Among other functions, the SDRAM probably acts as a "shadow" for the direct execution of system code that the NANDflash memory stores.

Above the SDRAM and an intermediary piece of cushioning foam are two 1-Gbyte Samsung K9K8G08U0M NAND-flash-memory devices on a double-sided daughtercard. This modular arrangement gives Sandisk the flexibility to leverage a common primary-PCB design across multiple Sansa M200 family proliferations-having 512-Mbyte, 1-Gbyte, and 4-Gbyte capacities-and to source NAND-flash memories in multiple IC-density, architecture, and supplier variations.

POWERED WITH ELECTRICITY, GAS,

AND AUTOMATICALLY-GENERATED CODE.

THAT'S MODEL-BASED DESIGN.

To create a two-mode hybrid powertrain, engineers at GM used models to continuously verify their design, test prototypes, and automatically generate the embedded code.

The result: a breakthrough HEV, delivered on time.

To learn more, visit mathworks.com/mbd

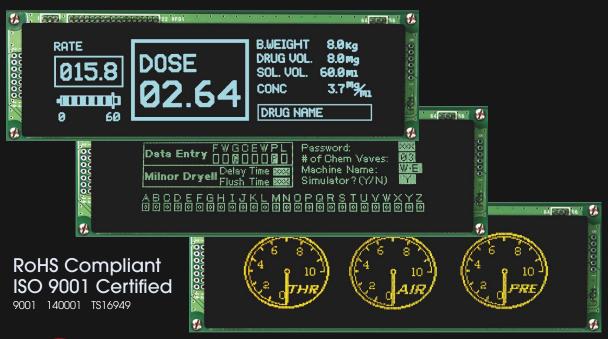

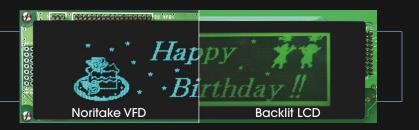

## Noritaker

## Graphic Display Value

## Approaching Character Display Prices

## A Display You Can Read From Any Angle

## MORE

#### Noritake 7000 Series

#### Built-in features than you may ever need...

- ▶ Up to 4 Independent Windows with Individual Control

- ▶ Many Int'l Font Sets with 16 User-Defined Characters

- ▶ Easily Combine Text & Graphics on One Screen

- ▶ Horizontal & Vertical Scrolling

- ▶ Proportional Fonts & Font Magnification

- ▶ 8 Levels of Brightness Control

- ▶ Built-in Screen Savers

- ▶ Many Filters Available to Match Application

- ▶ Development Kit Available

**DON'T COMPROMISE.**Your application deserves **VFD quality ...**

#### www.noritake-elec.com/11m

Noritake Co., Inc. 2635 Clearbrook Dr., Arlington Heights, IL 60005 phone 1-800-779-5846 e-mail electronics@noritake.com

BY ROBERT CRAVOTTA . TECHNICAL EDITOR

# DDING LIGHT O

EMBEDDED DEBUGGING GETS A LOT OF ATTENTION FOR BEING A SCHEDULE AND RESOURCE HOG. BUT THERE MAY BE MORE TO IT THAN JUST FIXING BAD SOFTWARE.

or each year of Embedded Systems Design's annual market survey of embedded-system developers, the single most requested area of improvement for design activities is debugging tools (Reference 1). The percentage of respondents making this request has remained steady at around 32% throughout the three years of the survey. In contrast, the percentage of respondents seeking improved programming tools has dropped from a high of 25% to 10%. Determining why the evolution of modern debugging tools is failing to hit the mark as well as software-programming tools do is worth

exploring—especially when the surveys each year also confirm that the testingand-debugging phase continues to be the one that consumes the largest amount— 24%—of the project schedule. The third standout request for improvement in all three years' surveys is the project-management function of scheduling (see sidebar "COCOMO and evidence-based scheduling").

One explicit aspect of engineering is

to create systems that perform and deliver a practical approach to a problem. Software-programming tools focus on the creation side of software engineering. The survey results suggest that programming tools are on the right path toward improving productivity for the creation of system code to solve problems. But the failure of debugging tools to trend downward as a primary concern alongside programming tools suggests that software-debugging tools are not merely extensions of programming tools that help developers correct mistakes or incorrect coding.

There is a less obvious, almost implicit aspect of engineering—that designers must not only design systems that perform some desirable function, but also eliminate or mitigate undesirable behaviors that may result from uncertainty and variability in the environment, so that the system behaves consistently across a range of operating conditions. This hidden side of engineering potentially provides insight into the challenges facing software-debugging tools, especially for embedded-system designers. In addition to dealing with processor-architecture practical constraints for performance, function, communication, latency, and power consumption, embedded systems often have to deal with real-world interfaces that may exhibit behaviors that are more difficult to predict or characterize completely across the whole range of usage scenarios.

If debugging were only about finding and correcting software-logic errors, an instruction-set simulator in conjunction with cycle-accurate simulators might provide enough visibility into the behavior of embedded systems to support debugging. Such simulators are available for most processor architectures and software-development-tool suites. Simulators can also stop the system and examine any parts of the simulated system. Unfortunately, these types of simulators usually cannot provide complete visibility into the exact interaction and latency of the memory, bus architectures, peripherals, sensors, and actuators. Such fidelity would make the simulators operate even slower than they already do.

System-level simulators, such as the virtual-system-prototype tools from Vast and the Simics virtual platform from Virtutech, have the potential to go be-

#### AT A GLANCE

- ▶ Engineering embedded systems is not just about making them perform some behavior but preventing them from exhibiting undesirable behavior.

- Designers may be using debugging tools as design aids because there are no other better means for doing the job.

- Debugging embedded systems is a cross-disciplinary activity, crossing hardware, software, and domain-expertise boundaries.

yond the software-execution engine and simulate the interactions of the other parts of the system. These types of development tools can enable software developers to work on a target before the physical hardware is available; they also can assist developers with system integration and testing efforts by supporting system-level fault injection and incremental integration in parallel to other development activities. These types of systems can act as precursors or support to hardware-in-the-loop simulations for high-end, complex systems. These tools support prebuilt systems and assembling a system from prebuilt parts or blocks. With additional tooling, they offer the ability to build new components to integrate into the system.

One hurdle system-level simulators face is cost, which can exceed by many thousands of dollars the price of available processor-centric simulators. It is possible that debugging tools are not following the downward trend in the surveys with programming tools not because they are failing to meet the functional needs of embedded-system developers, but rather because the higher-end

#### COCOMO AND EVIDENCE-BASED SCHEDULING

Realistic schedules are keys to creating good software. Deadlines that are too tight create avoidable stress sources that could lead to shipping an incomplete project. Recognizing that a deadline is too tight forces you to focus on the best or the most important features first, and it helps you to make the right decisions about what to incorporate into the final product. There have been a number of approaches to helping project managers produce more accurate schedules that trade off features, cost, and time for software-development projects.

One such approach is COCOMO (constructive-cost model), an algorithmic-software-cost-estimation model that applies a regression formula with historical project data and current project characteristics. Software engineer Barry Boehm first published the model in 1981.

The COCOMO II model incorporates changes in software development over the years to estimate the cost, effort, and schedule when planning new software-development projects. The COCOMO II model is available to the public from the University of Southern California Center for Systems and Software Engineering Web site (Reference A).

**COCOMO II comprises** application-composition, early-design, and postarchitectural submodels that provide increasing fidelity according to how far the project-planning and -design process has proceeded, COCOMO II can assist with setting project budgets and schedules; making software-cost and schedule-risk-management decisions; making trade-offs among software cost, schedule, functions, performance, and quality factors; and deciding which parts of a software system to develop, reuse,

lease, or purchase. A key factor in continuing to improve the predictive accuracy of COCOMO II is good data. The COCOMO II research group is asking for help from the software industry to collect data from development projects; the data collection will enable the availability of a more accurate predictive model for estimating software-project costs.

Another approach for incorporating historical data into the schedule modeling appears in a posting by Joel Spolsky, chief executive officer of Fog Creek Software, on evidence-based scheduling (Reference B). The article describes the approach for the model in a general fashion, although Fog Creek uses the model in its FogBugz commercial product. The first step is scheduling in chunks that you measure in hours-for example, no more than 16 hours to ensure the estimator has actually

thought about the steps necessary to complete a task. By keeping time sheets, you can compare estimates with the actual results from each developer and establish estimate-scaling velocities that will not only help you improve your estimates over time, but also provide vou a model for Monte Carlo simulation to calculate and chart the probability that you will be able to ship by any given date. Armed with the charted probable-shipping dates, you can explore how shifting the priorities of different features or including changes in scope may affect the schedule.

#### REFERENCES

- A "COCOMO II," http:// sunset.usc.edu/csse/ research/COCOMOII/ cocomo\_main.html.

- Spolsky, Joel, "Evidence Based Scheduling," Joel on Software, Oct 26, 2007, www.joelonsoftware.com/ items/2007/10/26.html.

## The world standard.

TDS3000 Series 100 to 500 MHz

DPO70000/DSA70000 Series 4 to 20 GHz

TDS1000/TDS2000 Series 40 to 200 MHz

DPO7000 Series 500 MHz to 3.5 GHz

DPO3000 Series 100 to 500 MHz

DSA8000 Series DC to 70+ GHz

DPO4000/MSO4000 Series 350 MHz to 1 GHz

## 8 out of 10 engineers the world over rely on Tektronix oscilloscopes to help them meet their design goals. So can you.

The vast majority of engineers depend on the industry-leading performance, precision, flexibility, ease-of-use and reliability of Tektronix oscilloscopes, software applications and accessories. In short, they set the standard by which all others are judged. Our broad portfolio includes everything from complete debug and analysis to the most advanced acquisition engines, including the 20 GHz DPO72004 and DSA72004, the world's fastest real-time scopes. In fact, Tektronix has remained an innovator in test and measurement for over 60 years. So rely on a Tektronix scope, and the experts standing behind it, to help you take on the world.

The best scopes on the planet.

Download the product catalog at: www.tektronix.com/catalog

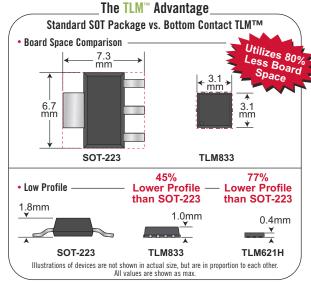

#### Central's new Tiny Leadless Modules™ (TLM™)

Designed for today's ultra thin electronic products, Central Semiconductor Corp. introduces the TLM™ (Tiny Leadless Module) family. The TLM™ packages feature lower profile (height) and utilize less board space as compared to standard SOT packages. Find below several featured devices from this new family:

#### Rectifiers

| Central<br>Type No. | I <sub>F</sub> | V <sub>RRM</sub><br>(V) | Description      | TLM Size<br>L x W x H<br>(mm) | Package |

|---------------------|----------------|-------------------------|------------------|-------------------------------|---------|

| *CTLSH1-40M621H     | 1.0            | 40                      | Single, Schottky | 2 x 1.5 x 0.4                 | TLM621H |

| CTLSH1-40M832D      | 1.0            | 40                      | Dual, Schottky   | 3 x 2 x 0.9                   | TLM832D |

| CTLSH2-40M832       | 2.0            | 40                      | Single, Schottky | 3 x 2 x 0.9                   | TLM832  |

| CTLSH3-30M833       | 3.0            | 30                      | Single, Schottky | 3 x 3 x 0.9                   | TLM833  |

| CTLSH5-40M833       | 5.0            | 40                      | Single, Schottky | 3 x 3 x 0.9                   | TLM833  |

#### Transistors Centra

| Central<br>Type No.                     | lc  | VCBO | Description                    | LxWxH       | Package |

|-----------------------------------------|-----|------|--------------------------------|-------------|---------|

| .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | (A) | (V)  |                                | (mm)        |         |

| *CTLT3410-M621                          | 1.0 | 40   | Low V <sub>CE(SAT)</sub> , NPN | 2 x 1 x 0.8 | TLM621  |

| *CTLT7410-M621                          | 1.0 | 40   | Low V <sub>CE(SAT)</sub> , PNP | 2 x 1 x 0.8 | TLM621  |

| CTLT853-M833                            | 6.0 | 200  | High Current, NPN              | 3 x 3 x 0.9 | TLM833  |

| CTLT953-M833                            | 5.0 | 140  | High Current, PNP              | 3 x 3 x 0.9 | TLM833  |

#### Combo: Low VCE(SAT) Transistor and Low VF Schottky Rectifier

| Central              | Transistor         |                      | Rectifier          |                         | TLM Size          | Package |

|----------------------|--------------------|----------------------|--------------------|-------------------------|-------------------|---------|

| Type No.             | I <sub>C</sub> (A) | V <sub>CBO</sub> (V) | I <sub>F</sub> (A) | V <sub>RRM</sub><br>(V) | L x W x H<br>(mm) |         |

| CTLM1034-M832D (NPN) | 1.0                | 40                   | 1.0                | 40                      | 3 x 2 x 0.8       | TLM832D |

| CTLM1074-M832D (PNP) | 1.0                | 40                   | 1.0                | 40                      | 3 x 2 x 0.8       | TLM832D |

Central welcomes the opportunity to explore selected, special, or custom devices, upon request. \* Under Development

Call Today and experience the TLM Advantage.

For Samples visit: www.centralsemi.com/tlm3

or call 631-435-1110

Central

Semiconductor Corp.

www.centralsemi.com

Small Signal Transistors Bipolar Power Transistors Devices MDMs

TLMs Rectifiers Diodes Transient Voltage Suppressors MOSFETs

debugging tools with the needed functional support still exceed some critical cost threshold. It is interesting to note that this cost threshold is lower than that for hardware-design tools, even though most software-development tools will likely support more of the additional complexity in new systems.

The last decade has seen serious erosion in royalty-based operating-systemand development-tool-license models. The growing success of Linux as an operating system in embedded systems is due largely to the cost advantage of using open-source software. Additionally, many embedded-system tools from silicon providers have adopted the opensource Eclipse platform to host their development tools, which substantially reduces the cost of building these tools, simplifies configuring their tools by the end user, and allows them to focus their engineering effort on the features of the tools rather than the look and feel of the host environment. This observation is not to say that debugging tools have not followed the same downward trend in pricing. At the extreme, many processor vendors offer small evaluation kits that allow developers to experiment with the systems for much less than \$100. Indeed, many development kits that cost hundreds of dollars today include features you would find a decade ago only in much costlier tool sets.

As on-chip-debugging circuitry expands on contemporary processor architectures, the industry may continue to see the higher-end-debugging functions finding their way into lower-cost development-tool kits. Many processors, including small, 8-bit processors, contain some proprietary on-chip-debugging circuitry. "The on-chip-debug system is one of the most complex circuits in the chip because it has to non-intrusively interconnect with all of the subsystems," says Dag Arne Braend, AVR-developmenttool director at Atmel. "And it has been difficult to justify incurring the extra cost for this complexity for something that many systems will never use in field devices."

Real-time trace appears to be the next emerging on-chip-debugging capability moving down the processor hierarchy. Processors using ARM cores with an ETM (embedded-trace macrocell) enable the downloading of instruction and data traces from the processor. The THE LAST DECADE

HAS SEEN SERIOUS

EROSION IN ROYALTYBASED OPERATINGSYSTEM- AND

DEVELOPMENT-TOOLLICENSE MODELS.

Cortex-M3 core supports a new realtime-trace capability. Trace enables reverse-order instruction execution, which more simulators are supporting. The Green Hills Software Multi Time Machine debugging suite enables developers to swap between on-chip debugging and simulator debugging to support simulated reverse-order execution.

IEEE-ISTO 5001-2003, the Nexus 5001 Forum open industry standard for a global embedded-processor-debugging method, provides a general-purpose interface for the software development and debugging of embedded processors. The initial focus of the Nexus 5001 Forum was automotive power-train applications, but its result has evolved to become a general-purpose standard. The Nexus 5001 Forum membership spans the semiconductor, development-tool, and automotive-electronics industries. As the cost of silicon continues to drop and on-chip-debugging interfaces and functions become standard, processor providers will likely flow high-end onchip-debugging capabilities from highend processors to lower-end processors to provide even more on-chip visibility. This step will become necessary to gain design wins.

#### **DESIGN AID**

John Lambert, chief executive officer of Virtutech, offers an immediate possible mitigating factor for the higher costs in favor of system-level-simulation tools. "A development team usually acquires our platform to support either the front or the back end of its current proj-

the EVOLUTION of ANALOG™

interdi

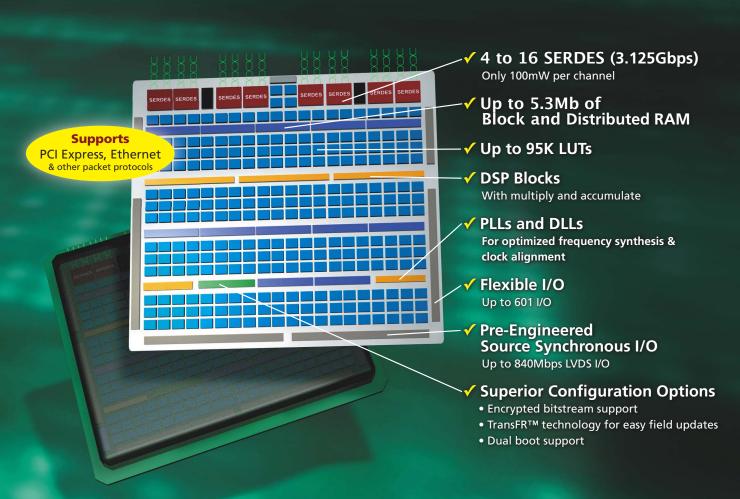

## Lattice ECP2IVI FPGAs More of the Best

## LatticeECP2M: The First Low-Cost FPGA with 3Gbps SERDES

Get more for less with Lattice's new LatticeECP2M™ family. No other low-cost FPGA offers up to 16 SERDES channels with full-duplex serial data transfers at rates up to 3.125Gbps. Best of all, each SERDES channel operates on a cool 100mW at maximum speed.

The LatticeECP2M family offers even more, including up to 5.3Mb of RAM, high-speed DSP blocks, 533Mbps DDR2 memory interface and SPI4.2 support. Plus, 128-bit AES Encrypted Bitstream support and Transparent Field Reconfiguration (TransFR™) allow you to keep your designs secure and easily upgradeable even after your product has shipped.

For design software and a FREE FPGA handbook go to latticesemi.com/ecp2m

LatticeECP2M FPGAs give you "More of the Best" for less. Visit our website at **www.latticesemi. com**. You'll find information about Lattice's complete line of FPGAs, including LatticeECP2M, LatticeECP2™, LatticeSC™ Extreme Performance System Chip FPGAs, LatticeXP™ non-volatile FPGAs and many more. If you haven't looked at Lattice FPGAs lately, look again — things have changed.

ect, but once the team uses the tool, it more fully realizes its value and uses it at both ends of the design cycle in future projects," he says.